# QSFP+

#### EQA854X-4DLC

#### 40Gb/s QSFP+ - 4x double LC connect

#### **QSFP+ AOC end:**

- Compliant to the 40GBASE-SR4 and XLPPI

- Specification per IEEE 802.3ba-2010 and supporting

- > 40G-IB-QDR / 20G-IB-DDR / 10G-IB-SDR applications

- > Compliant to the industry standard SFF-8436

- QSFP+ Specification

- Power Level 1: Max Power < 1.5 W</p>

- > Operate at 10.3125 Gbps per channel with 64b/66b

- encoded data for 40GbE application and at 10 Gbps

- with 8b/10b compatible encoded data for 40G-IB-QDR application

#### Each 4× Double LC Connect end:

> With double LC Single Mode connect, or double LC Muti-mode connect

#### **Active Optical Cable Assembly:**

- > 0 to 70 C degree case temperature operating range

- Proven High Reliability 850 nm technology: VCSEL transmitter and PIN receiver

- > Hot pluggable for ease of servicing and installation

- Two Wire Serial interface

Utilizes optical fiber for high density and thin, lightweight cable management

# FC ( E 🗵 🎱

## Applications

- > 40GbE and 10GbE break-out applications for Datacom switch and router connections

- > 40G to 4×10G density applications for Datacom and Proprietary protocol applications

- Datacenter

#### **Description**

The cable is a Four-Channel, Pluggable, Parallel, Fiber-Optic QSFP+ Active Optical Cable (AOC) to 4× double LC connect Cable break-out solution. This Breakout cable is intended for 40G to 4× 10G applications.

This AOC is a high performance cable for short-range multi-lane data communication and interconnect applications. It integrates four data lanes in each direction with 40 Gbps aggregate bandwidth. Each lane can operate at 10.3125 Gbps. These cables also support 4 x 10G InfiniBand QDR applications and are backwards compatible to the 4 × 5G IB DDR and 4 × 2.5G IB single IB SDR applications.

This product is leveraged from QSFP+ to QSFP+ Active Optical Cable product and SFP+ Active Optical Cable product. Where applicable, consult these respective datasheets

This AOC incorporates proven integrated circuit and VCSEL technology to provide reliable long life, high performance, and consistent service.

#### **Absolute Maximum Ratings**

The operation in excess of any absolute maximum ratings might cause permanent damage to this module.

| Parameter                         | Symbol | Min  | Max     | Unit | Note |

|-----------------------------------|--------|------|---------|------|------|

| Storage Temperature               | TST    | -40  | 85      | degC |      |

| Relative Humidity(non-condensing) | RH     | 0    | 85      | %    |      |

| Operating Case Temperature        | TOPC   | 0    | 70      | degC |      |

| Supply Voltage                    | VCC    | -0.3 | 3.6     | V    |      |

| Input Voltage                     | Vin    | -0.3 | Vcc+0.3 | V    |      |

#### **Recommended Operating Conditions and Supply Requirements**

| Parameter                    | Symbol | Min  | Typical | Max     | Unit |

|------------------------------|--------|------|---------|---------|------|

| Operating Case Temperature   | TOPC   | 0    |         | 70      | degC |

| Power Supply Voltage         | VCC    | 3.13 | 3.3     | 3.47    | V    |

| Data Rate                    | DR     |      | 10.3    | 11.3    | Gbps |

| Data Speed Tolerance         | ∆DR    | -100 |         | +100    | ppm  |

| Link Distance with OM3 fiber | D      | 0    |         | 100     | m    |

| Control* Input Voltage High  | Vih    | 2    |         | VCC+0.3 | V    |

| Control* Input Voltage Low   | Vil    | -0.3 |         | 0.8     | V    |

| I2C Serial Interface frequence    | fs |  | 400k | Hz   |

|-----------------------------------|----|--|------|------|

| Power Supply Noise                |    |  | 50   | mVpp |

| Receiver Differential Data Output |    |  |      |      |

| Load                              |    |  | 100  | mVpp |

#### **Active Cable-End Electrical Characteristics**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted. Typical values are for Tc = 40 °C, Vcc = 3.3 V

| Parameter                  | Symbol | Min | Typical | Max | Unit |

|----------------------------|--------|-----|---------|-----|------|

| QSFP+ 40G Active Cable-End |        |     |         |     |      |

| Power Consumption          |        |     |         | 1.5 | W    |

| QSFP+ 40G Active Cable-End |        |     |         |     |      |

| Power Supply Current       |        |     |         | 300 | mA   |

#### **QSFP+ AOC-end Electrical Characteristics Electrical**

#### **Specifications**

| Parameter                             | Symbol | Min     | Typical | Max  | Unit  |

|---------------------------------------|--------|---------|---------|------|-------|

| Differential input impedance          | Zin    | 90      | 100     | 110  | ohm   |

| Differential Output impedance         | Zout   | 90      | 100     | 110  | ohm   |

| Differential input voltage amplitude  | ΔVin   | 300     |         | 1100 | mVp-p |

| Differential output voltage amplitude | ΔVout  | 400     |         | 800  | mVp-p |

| Bit Error Rate                        | BR     |         |         |      | E-12  |

| Input Logic Level High                | VIH    | 2.0     |         | VCC  | V     |

| Input Logic Level Low                 | VIL    | 0       |         | 0.8  | V     |

| Output Logic Level High               | VOH    | VCC-0.5 |         | VCC  | V     |

| Output Logic Level Low                | VOL    | 0       |         | 0.4  | V     |

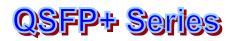

# QSFP+ AOC-end Pin Descriptions

| PIN | Logic      | Symbol  | Name/Description                     | Note |

|-----|------------|---------|--------------------------------------|------|

| 1   |            | GND     | Ground                               | 1    |

| 2   | CML-I      | Tx2n    | Transmitter Inverted Data Input      |      |

| 3   | CML-I      | Tx2p    | Transmitter Non-Inverted Data output |      |

| 4   |            | GND     | Ground                               | 1    |

| 5   | CML-I      | Tx4n    | Transmitter Inverted Data Input      |      |

| 6   | CML-I      | Tx4p    | Transmitter Non-Inverted Data output |      |

| 7   |            | GND     | Ground                               | 1    |

| 8   | LVTLL-I    | ModSelL | Module Select                        |      |

| 9   | LVTLL-I    | ResetL  | Module Reset                         |      |

| 10  |            | VccRx   | + 3.3V Power Supply Receiver         | 2    |

| 11  | LVCMOS-I/O | SCL     | 2-Wire Serial Interface Clock        |      |

| 12  | LVCMOS-I/O | SDA     | 2-Wire Serial Interface Data         |      |

| 13  |            | GND     | Ground                               |      |

| 14  | CML-O      | Rx3p    | Receiver Non-Inverted Data Output    |      |

| 15  | CML-O      | Rx3n    | Receiver Inverted Data Output        |      |

| 16  |            | GND     | Ground                               | 1    |

| 17  | CML-O      | Rx1p    | Receiver Non-Inverted Data Output    |      |

| 18  | CML-O      | Rx1n    | Receiver Inverted Data Output        |      |

| 19  |            | GND     | Ground                               | 1    |

| 20  |            | GND     | Ground                               | 1    |

| 21  | CML-O      | Rx2n    | Receiver Inverted Data Output        |      |

| 22  | CML-O      | Rx2p    | Receiver Non-Inverted Data Output    |      |

| 23  |            | GND     | Ground                               | 1    |

| 24  | CML-O      | Rx4n    | Receiver Inverted Data Output        | 1    |

| 25  | CML-O      | Rx4p    | Receiver Non-Inverted Data Output    |      |

| 26  |            | GND     | Ground                               | 1    |

| 27  | LVTTL-O    | ModPrsL | Module Present                       |      |

| 28  | LVTTL-O    | IntL    | Interrupt                            |      |

| 29  |            | VccTx   | +3.3 V Power Supply transmitter      | 2    |

| 30  |            | Vcc1    | +3.3 V Power Supply                  | 2    |

| 31  | LVTTL-I    | LPMode  | Low Power Mode                       |      |

| 32  |            | GND     | Ground                               | 1    |

| 33  | CML-I      | Тх3р    | Transmitter Non-Inverted Data Input  |      |

| 34  | CML-I      | Tx3n    | Transmitter Inverted Data Output     |      |

| 35  |            | GND     | Ground                               | 1    |

| 36 | CML-I | Tx1p | Transmitter Non-Inverted Data Input |   |

|----|-------|------|-------------------------------------|---|

| 37 | CML-I | Tx1n | Transmitter Inverted Data Output    |   |

| 38 |       | GND  | Ground                              | 1 |

5

#### Notes:

- 1) Module circuit ground is isolated from module chassis ground within the module. GND is the symbol for signal and supply (power) common for QSFP modules.

- 2) The connector pins are each rated for a maximum current of 500mA.

#### **ModSelL Pin**

The ModSelL is an input pin. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP modules on a single 2-wire interface bus. When the ModSelL is "High", the module will not respond to any 2-wire interface communication from the host. ModSelL has an internal pull-up in the module.

## ResetL Pin

Reset. LPMode\_Reset has an internal pull-up in the module. A low level on the ResetL pin for longer than the minimum pulse length (t\_Reset\_init) initiates a complete module reset, returning all user module settings to their default state. Module Reset Assert Time (t\_init) starts on the rising edge after the low level on the ResetL pin is released. During the execution of a reset (t\_init) the

host shall disregard all status bits until the module indicates a completion of the reset interrupt. The module indicates this by posting an IntL signal with the Data\_Not\_Ready bit negated. Note that on power up (including hot insertion) the module will post this completion of reset interrupt without requiring a reset.

#### **LPMode Pin**

QSFP+ SR4 operate in the low power mode (less than 1.5 W power consumption) This pin active high will decrease power consumption to less than 1W.

#### ModPrsL Pin

ModPrsL is pulled up to Vcc on the host board and grounded in the module. The ModPrsL is asserted "Low" when the module is inserted and deasserted "High" when the module is physically absent from the host connector.

#### IntL Pin

IntL is an output pin. When "Low", it indicates a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt by using the 2-wire serial interface The IntL pin is an open collector output and must be pulled up to Vcc on the host board.

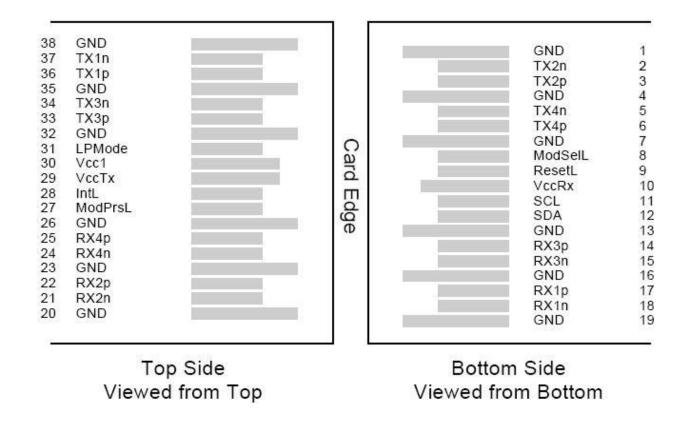

## **QSFP+ AOC-end Power Supply Filtering**

The host board should use the power supply filtering shown in Figure 1.

## QSFP+ AOC-end EEPROM Serial ID Memory Contents

Compliant to the industry standard SFF-8436 QSFP+ Specification

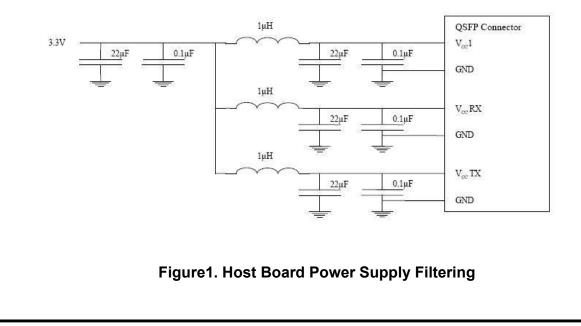

## **QSFP+ AOC-end Power Supply Filtering**

NOTE: INDUCTORS MUST HAVE LESS THAN 1 $\Omega$  series resistance to limit voltage drop to the SFP module.

## **Optical Fiber Specifications**

| Parameter                | Specification                |

|--------------------------|------------------------------|

| Tight buffer color       | Blue                         |

| Tight buffer material    | PVC                          |

| Fiber type               | 62.5/125 (OFS)               |

|                          | Bandwith:160 MHz.km @ 850 nm |

| Jacket material          | PVC                          |

| Cable diameter mm        | 3.0 ± 0.1                    |

| Cable weight Kg/km       | 7.0                          |

| Min. bending radius mm   | 30                           |

| Attenuation dB/km        | ≤ 3.5 at 850 nm              |

|                          | ≤ 1.5 at 1300 nm             |

| Short tension N          | 120                          |

| Operation temperature °C | -20~70                       |

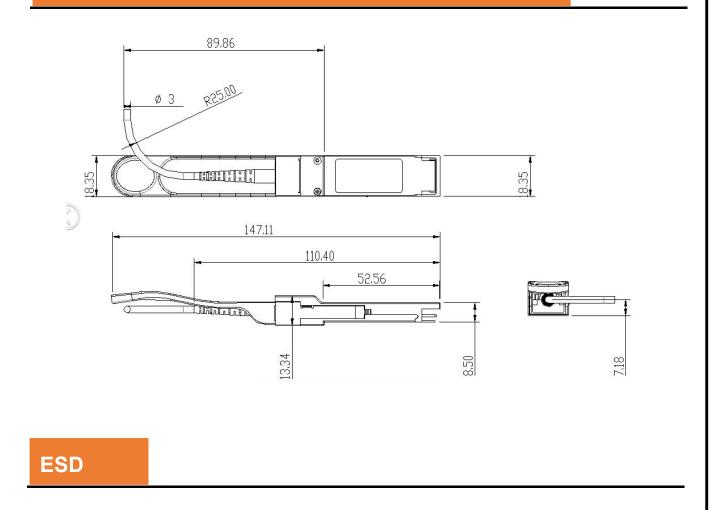

#### **QSFP+ AOC end Mechanical Specifications**

This transceiver is specified as ESD threshold 1KV for high speed data pins and 2KV for all others electrical input pins, tested per MIL-STD-883, Method 3015.4 /JESD22-A114-A (HBM). However, normal ESD precautions are still required during the handling of this module. This transceiver is shipped in ESD protective packaging. It should be removed from the packaging and handled only in an ESD protected environment.

#### Laser Safety

This is a Class 1 Laser Product according to IEC 60825-1:2007. This product complies with 21 CFR 1040.10 and 1040.11 except for deviations pursuant to Laser Notice No. 50, dated (June 24, 2007)

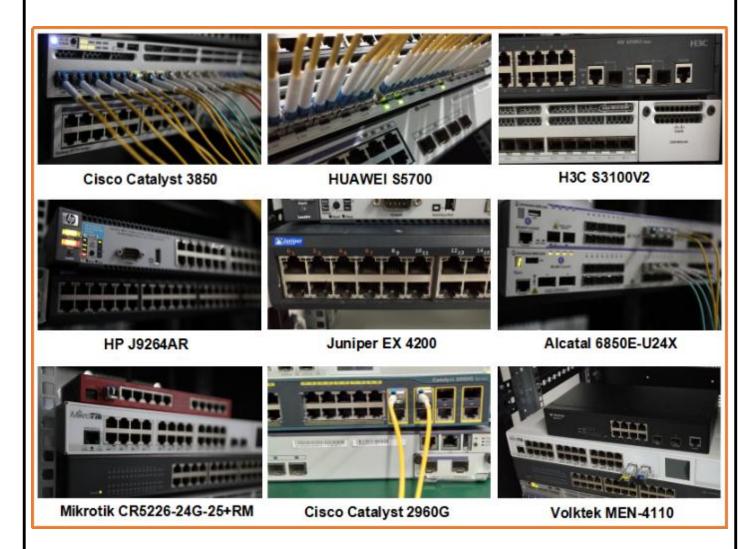

#### **Compatibility Test**

In order to ensure the product compatibility, our products will be tested on the switch before shipment. Our modules can compatible with many mainstream brand switches, such as Cisco, Juniper, Extreme, Brocade, IBM, H3C, HP, Huawei, D-Link, Mikrotik, ZTE, TP-Link...

Our test equipment: VOLKTEK MEN-4110, HP 2530-8G, CRS226-24G-25+RM, Catalyst 2960G Series, Catalyst 3850 XS 10G SFP+, Catalyst 3750-E Series, HUAWEI S5700Series, H3C S3100V2 Series, Juniper-EX4200, etc.

## **Product Production Process**

# **Quality Assurance**

Continuous introduction of new equipment, produced by strict standards, strict quality inspection, to guarantee the high quality standard of each product.

#### Packaging

#### Individual package.

Company: ETU-Link Technology Co., LTD Address:4th Floor, C Building, JinBoLong Industrial Park, QingQuan Road, LongHua District, Shenzhen city, GuangDong Tel: +86-755 2328 4603

Addresses and phone number also have been listed at www.etulinktechnology.com. Please e-mail us at sales@etulinktechnology.com or call us for assistance.

Fiber Optic Transceivers Copyright 2011—2017 etulinktechnology.com All Rights Reserved